Digital Larry

Well-known member

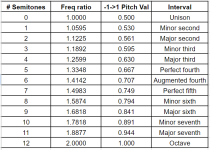

I think I suggested that you try the Pitch Up Down block in a response to one of your other messages. If I remember correctly it puts out one octave up and one octave down at the same time. I'm sorry I don't take requests to build patches but it should be fairly easy to put together.Hello, thank you, and I apologize for bothering you. My dear friend. I have a question for you. I'm going to use this on the FV-1. Could you send me a SpinCad algorithm that allows you to move the same note up and down a few octaves without changing the pitch, just like the octave boost module effects found on piano organs? Or what algorithm should I use for this?

DL