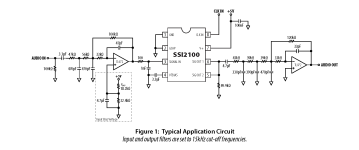

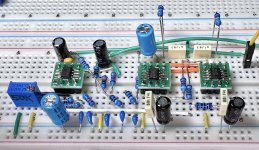

I've had mixed results. I'm not sure how reliable the schematic in the datasheet is, I've asked SS for details of their demo board that they showed at NAMM.

Asking Claude about the example schematic confirmed many of the biasing and reference voltage issues that I had.

"Good question — having just worked through all these issues on your board, several of them trace directly back to ambiguities or outright errors in the datasheet circuit.

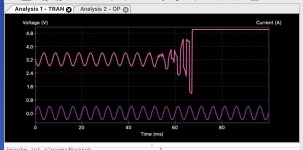

Single supply claimed, split supply assumed. The front page lists "Single 5V Operation" as a feature, but the output TL072's non-inverting input is tied straight to ground. That only works with a split supply where ground is mid-rail. On actual single 5V, U2B rails low — exactly the problem you hit. There's no note acknowledging this inconsistency.

No DC bias on the output reconstruction filter. After the 4.7µF AC coupling cap, all the shunt elements (330pF, 390pF, 470pF) are capacitors. There's no resistive DC path anywhere in the filter to set the operating point. Again, this works fine on split supply where the ground-referenced + input clamps things, but on single supply the node floats — as you discovered at 4.2V.

No feedback path shown at all. For a delay chip, the absence of any delay feedback topology in the "typical application" is a significant omission. It's arguably the most important part of the application circuit for a pedal designer, and it's the bit that causes the most DC biasing headaches (as you've found). Even a dashed-line "optional feedback" section would have saved a lot of grief.

RBIAS source impedance. The 18.2K/32.4K divider has a Thévenin impedance of about 11.6K. The datasheet text says pin 3 needs a "low impedance source" because of the sampling transients, and they do show the 100Ω/1nF isolation network, but the bias itself is feeding through the entire input filter chain (56K + 33K in series). The interaction between the bias impedance and the filter response isn't discussed.

No decoupling guidance for the op-amps. The circuit shows 100nF on the SSI2100's V+ pin but nothing on the TL072 supply pins. For a circuit processing microvolt-level signals with a clock running at up to 2MHz, that's an oversight — you've already added C20/C21 which is the right call.

Honestly, it reads like the application circuit was designed assuming ±5V rails and then the "single 5V" feature was added to the marketing without updating Figure 1 to match."