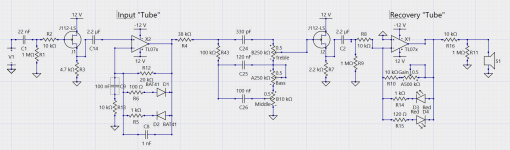

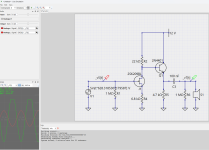

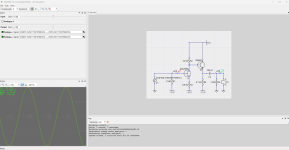

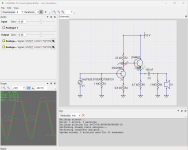

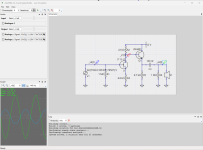

Hey folks, I've been designing this Blackface-ish inspired preamp circuit. The thing is it inverts the output which I want to avoid. For stubborn reason I've been trying to avoid using another op amp for the task of re-inverting the signal, adding a bit of gain, and buffering the output. I've been using this circuit which works well enough but one half of the waveform buts up against the 12v rail. Given that I have -12v available as well I'm sure there must be a way to leverage that to make biasing easier. Honestly maybe the solution is just to use an op-amp, but either way I would like to learn about using discrete circuits with split rail.